可靠性

由于系统构成串联系统时,其中任何一个子系统失效就足以使系统失效,其可靠度等于各子系统可靠度的乘积。

构成并联系统时,只要有一个子系统正常工作,系统就能正常工作。设每个子系统的可靠性分别以R1,R2 ... RN表示,则并联系统的可靠度为:

R=1-(1-R1)(1-R2)(1-R3)...(1-R)

因此,本系统的可靠度为R(1-(1-R)2)2

更新时间:2023年10月11日 17:46:32

总线系统

在计算机系统中采用总线结构,便于实现系统的积木化构造,同时可以( )。

提供数据传输速度

提高数据传输量

减少信息传输线的数量

减少指令系统的复杂性

总线是在计算机中连接两个或多个功能部件的一组共享的信息传输线,它的主要特征就是多个部件共享传输介质。它是构成计算机系统的骨架,是各个功能部件之间进行信息传输的公共通道,借助总线的连接,计算机各个部件之间可以传送地址、数据和各种控制信息。在计算机系统中采用总线结构,便于实现系统的积木化构造,同时可以有效减少信息传输线的数量。

更新时间:2023年10月12日 22:35:26

流水线的计算

若指令流水线把一条指令分为取值、分析和执行三部分,且三部分的时间分别是取值2ns、分析2ns、执行1ns。

流水线周期是多少?

100条指令全部执行完备需要多少时间?

流水线的吞吐率是多少?

流水线的周期为花费时间最长的阶段所花费的时间,所以流水线的周期就是2ns。

根据理论公式,T=(2+2+1)+(100-1)*2=5+99*2=203ns

根据实践公式,T=(3+100-1)*2=204ns

理论吞吐率:TP=100/203

实际吞吐率:TP=100/204

①关于流水线的周期,我们需要知道的是,流水线周期(△t)为指令执行阶段中执行时间最长的一段。

②流水线的计算公式为:

完成一条指令所需的时间+(指令条数-1)*流水线周期,在这个公式中,又存在理论公式和实践公式。

理论公式:( t1 + t2 + ... + tn)+(n-1)× △t

实践公式:( k + n - 1)× △t k为一条指令所包含的部分的多少

③吞吐率的计算公式为:

TP=n/Tk=n/(kΔt+(n−1)Δt)

更新时间:2023年10月13日 17:25:49

存储系统

计算机系统的主存主要是由(5)构成的。

DRAM

SRAM

Cache

EEPROM

主存主要采用动态随机存储器DRAM

Cache采用静态随机存储器SRAM

EEPROM是电擦除可编程的只读存储器

更新时间:2023年10月18日 17:47:58

高速缓存Cache

(2017年下半年上午试题6)以下关于Cache(高速缓冲存储器)的叙述中,不正确的是( A )。

Cache的设置扩大了主存的容量

Cache的内容是主存部分内容的拷贝

Cache的命中率并不随其容量增大线性地提高

Cache位于主存与CPU之间

更新时间:

(2016年下半年上午试题6)一下关于Cache与主存间地址映射的叙述中,正确的是( D )。

操作系统负责管理Cache与主存之间的地址映射

程序员需要通过编程来处理Cache与主存之间的地址映射

应用软件对Cache与主存的地址映射进行调度

有硬件自动完成Cache与主存之间的地址映射

更新时间:

主存与Cache的地址映射方式中,( )方式可以实现主存的任意一块装入Cache中任意位置,只有装满才需要替换。

全相联

直接映射

组相联

串并联

全相联映射:各主存块可以映射到cache的任意数据块。

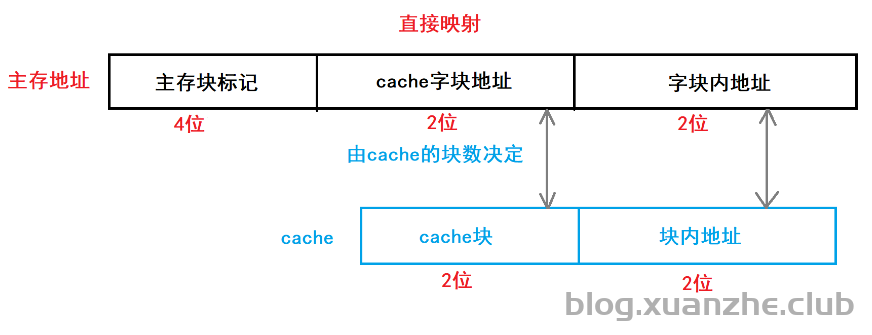

直接相连映射:各主存块只能映射到cache中的固定块。

组相连映射:各主存块只能映射到cache固定组中的任意块。

更新时间:2023年10月18日 13:40:30

某内存64块,cache有4块,一个块为4个字节,按字节编址。

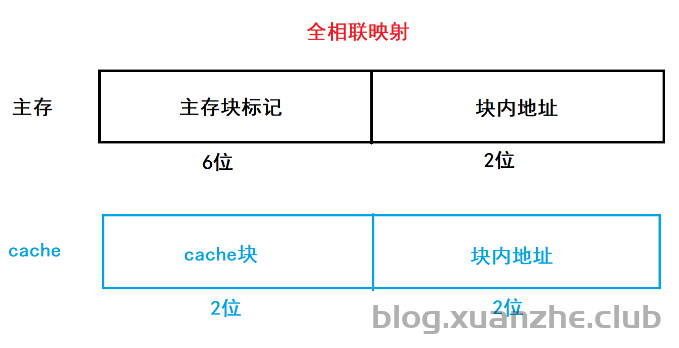

采用全相联映射方式,写出cache和主存地址格式。

采用直接映射方式,写出cache和主存地址格式。

全相联映射方式中主存的主存块标记是全部块标记,

根据主存和cache的对应关系,一个块为4个字节,能得出主存和cache的块内地址的位数都是2位,根据cache的块数是4,得出cache块的位数是2。

因为主存的块数为64块,得出主存块标记的位数是6位。

cache:4块=4*4字节=2的4次方字节,cache的总位数是4。

主存:64块=64*4字节=2的8次方字节,主存的总位数是8

由题意得:一个块4个字节,就是2的2次方,可以得出cache的块内地址为2位,又因为cache的总位数是4,所以得出cache块有(4-2)位

更新时间:2023年10月18日 17:26:47

主存的编址

内存地址从AC000H到C7FFFH,共有( )K个地址单元,如果该内存地址按字(16bit)编址,由28片存储器芯片构成。已知构成此内存的芯片每片有16K个存储单元,则该芯片每个存储单元存储( )位。

A. 96 B. 112 C. 132 D. 156

A. 4 B. 8 C. 16 D. 24

地址单元数量:

十六进制计算:C7FFF - AC000 + 1 = C8000 -AC000 = 1C000

十进制:(1C000)16 = ( 1 × 164 + 12 × 163 )÷ 1024 =( 1 × 164 + 12 × 163 )÷ ( 4 × 162 ) = 16 × 4 + 3 × 16 = 112

单元存储数量:

112 × 16 ÷ 28 × 16 = 4

更新时间:2023年10月18日 13:11:21

存储管理

分页存储管理

进程P有6个页面,页号为0~5,页面大小为4K,页面变换表如下所示。表中状态位等于1和0分别表示页面存在内存和不存在内存。假设系统给进程P分配了4个存储块,进程P要访问的逻辑地址为十六进制5A29H,那么该地址经过变换后,其物理地址应为十六进制 (1);如果进程P要访问的页面4不在内存,那么应该淘汰页号为 (2)的页面。

| 页号 | 页帧号 | 状态位 | 访问位 | 修改位 |

| 0 | 2 | 1 | 1 | 0 |

| 1 | 3 | 1 | 0 | 1 |

| 2 | 5 | 1 | 1 | 0 |

| 3 | - | 0 | 0 | 0 |

| 4 | - | 0 | 0 | 0 |

| 5 | 6 | 1 | 1 | 1 |

(1)A. 1A29H B. 3A29H C. 5A29H D. 6A29H

(2)A. 0 B. 1 C. 2 D. 5

(1)查表可知:页号5对应的物理块号为6,十六进制为:6H,把原来的5A29H中的5换成6即可(因为其页内地址不变),即最终物理地址为:6A29H

(2)查表可知:在内存的页有0、1、2、5,被访问过的页有1、2、5,被淘汰的页首先必须在内存中,淘汰的页号是最近没有被访问的页号,最后是没有修改的页号,即应该淘汰的页号为:1

更新时间:2023年10月18日 18:12:22

页面置换算法

假设系统为某进程分配了三个内存块,并考虑到有以下页面号引用串(会依次访问这些页面):7,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,7,0,1

最佳置换算法(OPT,optimal):每次选择淘汰的是以后永不使用,或者在最长时间内不再被访问的页面,这样可以保证最低的缺页率。

| 访问页面 | 7 | 0 | 1 | 2 | 0 | 3 | 0 | 4 | 2 | 3 | 0 | 3 | 2 | 1 | 2 | 0 | 1 | 7 | 0 | 1 |

| 内存块1 | 7 | 7 | 7 | 2 | 2 | 2 | 2 | 2 | 7 | |||||||||||

| 内存块2 | 0 | 0 | 0 | 0 | 4 | 0 | 0 | 0 | ||||||||||||

| 内存块3 | 1 | 1 | 3 | 3 | 3 | 1 | 1 | |||||||||||||

| 是否缺页 | √ | √ | √ | √ | √ | √ | √ | √ | √ |

更新时间:2023年10月18日 18:37:21

输入输出技术

计算机系统中常用的输入/输出控制方式有无条件传送、中断、程序查询和DMA方式等。当采用( )方式时,不需要CPU执行程序指令来传送数据。

中断

程序查询

无条件传送

DMA

程序控制输入输出方法主要有四种:

中断

程序查询:利用查询方式进行输入/输出,就是通过CPU执行程序来查询外设的状态,判断外设是否准备好接收数据或准备好向CPU输入数据。根据这种状态,CPU有针对地为外设的输入/输出服务。

无条件传送:可以无条件地随时接收CPU发来的输出数据,也能够无条件地随时向CPU提供需要的输入数据。

DMA(直接内存存取):是指数据在内存与I/O设备间的直接成块传送,即在内存与I/O设备间传送一个数据块的过程,不需要CPU的任何干涉,是一种完全由DMA硬件完成I/O操作的方式。

更新时间:2023年10月20日 10:49:55

校验码

以下关于检验码的叙述中,正确的是( A )。(2009下半年)

海明码利用多组数位的奇偶性来检错和纠错

海明码的码距必须大于等于1

循环冗余校验码具有很强的检错和纠错能力

循环冗余校验码的码距必定为1

海明码的码距必须大于1,等于2可以检错,大于等于3可能纠错

循环冗余校验码的码距等于2,只能检错,不能纠错

更新时间:2023年10月20日 11:10:49

奇偶校验码

以下关于采用奇偶校验方法的叙述中,正确的是( C )。(2018年下半年)

若所有奇数位出错,则可以检测出错误但无法纠正错误

若所有偶数位出错,则可以检测出错误并加以纠正

若有奇数个数据位出错,则可以检测出该错误但无法纠正错误

若有偶数个数据位出错,则可以检测出该错误并加以纠正

奇偶校验码的码距为2 ,所以可以检出1位错或奇数位错,无纠错能力 。

更新时间:2023年10月20日 13:14:12

海明码

以下关于海明码的叙述中,正确的是( A )

海明码利用奇偶性进行检错和纠错

海明码的码距为1

海明码可以检错不能纠错

海明码中数据位的长度必须与校验位相同

已知数据信息为16位,最少应附加( )位校验位,已实现海明码纠错。(2016年下半年)

3

4

5

6

2k -4 ≥ 16 +k

2k - k ≥ 20

k ≥ 5

海明码(Hamming Code)是由贝尔实验室的Richard Hamming设计的,是一种利用奇偶性来检错和纠错的校验方法。海明码的构成方法是在数据之间的特定位置上插入k个校验位,通过扩大码距来实现检错和纠错。

设数据位为 n 位,校验位是 k 位,则 n 和 k 必须满足以下关系:

更新时间:2023年10月20日 11:01:35

海明码利用奇偶性检错和纠错,通过在n个数据位之间插入k个校验位,扩大数据编码的码距。若 n=48,则 k 应该(至少)为( 6 )。(2014年上半年)

已知数据信息为16位,至少应附加( 5 )位校验位,以实现海明纠错码。(2016年下半年)

以10位数据为例,其海明码表示为D9D8D7D6D5D4P4D3D2D1P3D0P2P1中,其中Di(0 ≤ i ≤ 9)表示数据位,Pj(1 ≤ j ≤ 4)表示检验位,数据位D9由P4、P3和P2进行校验(从右至左D9的位序为14,即等8+4+2,因此用第8位的P4、第4位的P3和第2位的P2校验),数据位D5由( B )进行校验。(2018年上半年)

P4P1

P4P2

P4P3P1

P3P2P1

| D9 | D8 | D7 | D6 | D5 | D4 | P4 | D3 | D2 | D1 | P3 | D0 | P2 | P1 |

| 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

D5 P4 P2

10 = 8 + 2

更新时间:2023年10月21日 15:40:58

RISC与CISC

| RISC(精简指令计算机) | CISC(复杂指令计算机) | |

| 指令种类 | 少、精简 | 多、丰富 |

| 指令复杂度 | 简单 | 复杂 |

| 指令长度 | 固定 | 变化 |

| 寻址方式 | 少 | 复杂多样 |

| (译码)实现方式 | 硬布线控制逻辑(组合逻辑控制器) | 微程序控制技术 |

| 通用寄存器数量 | 多、大量 | 一般 |

| 流水线技术 | 适合 | 不适合 |